The current workaround we have is to apply sed -i '/^use work/b s/main_types\.//g' to this type file, after which Synplify Pro works just fine.

Do these even need to be qualified anyway? Is it ever ambiguous what they refer to? If so, maybe Clash could have a flag to opt in to generate unqualified names.

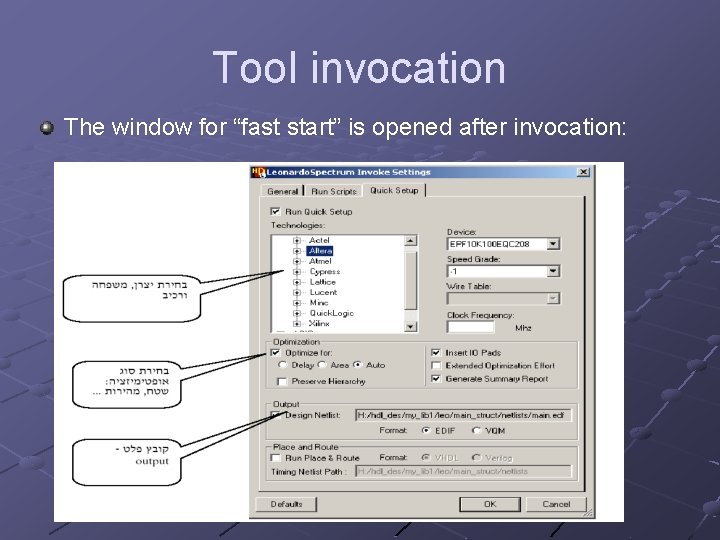

#VIVADO USE SYNPLIFY PRO CODE#

But it would be nice for Clash to generate code without these qualified names. Pro's: compiling a project via Verilator, and finding synthesis errors, can be done in seconds, vice minutes with Vivado. It could very well just be an issue with that tool, since Vivado and Quartus are happy with such VHDL. Drawbacks: Verilator is Verilog and System Verilog only, and things the Verilate don't always synthesize using Vivado. A design constructed strictly using generic RTL, which does not contain FPGA vendor-specific code or instantiations, can easily be ported from one FPGA vendor by simply retar-geting to the other FPGA vendor. The issue as far as I understand it is that Synplify Pro doesn't like qualified/namespaced names used inside of the namespace definition itself. The Synplify Pro and Synplify Premier so ftware contains HDL support that handles design portability and mixed HDL languages. > /nix/store/94wz1fddc9swincshkykr1rric41dwsm-virtual-simple-src/rtl/vhdl/Main/main_types.vhdl:31:54ģ1 | function fromSLV (slv : in std_logic_vector) return main_types.tup2 is > /nix/store/94wz1fddc9swincshkykr1rric41dwsm-virtual-simple-src/rtl/vhdl/Main/main_types.vhdl:14:54ġ4 | function fromSLV (slv : in std_logic_vector) return main_types.tup2 Package body main_types is function toSLV (s : in signed) return std_logic_vector is begin return std_logic_vector(s) įunction fromSLV (slv : in std_logic_vector) return signed is alias islv : std_logic_vector( 0 to slv 'length - 1) is slv įunction toSLV (p : main_types.tup2) return std_logic_vector is begin return (toSLV(p.tup2_sel0_signed_0) & toSLV(p.tup2_sel1_signed_1)) įunction fromSLV (slv : in std_logic_vector) return main_types.tup2 is alias islv : std_logic_vector( 0 to slv 'length - 1) is slv īegin return (fromSLV(islv( 0 to 63)),fromSLV(islv( 64 to 127))) Tup2_sel1_signed_1 : signed( 63 downto 0) įunction toSLV (s : in signed) return std_logic_vector įunction fromSLV (slv : in std_logic_vector) return signed įunction toSLV (p : main_types.tup2) return std_logic_vector įunction fromSLV (slv : in std_logic_vector) return main_types.tup2 Tup2_sel0_signed_0 : signed( 63 downto 0) Package main_types is type tup2 is record

0 kommentar(er)

0 kommentar(er)